TSMC Details Technology Roadmap With Multiple Offerings to Benefit Future Apple DevicesAs part of its recent

Q1 earnings call, TSMC announced that its 7-nanometer FinFET process node has entered into high volume manufacturing (HVM), meaning we could see consumer devices featuring the process as soon as the second half of this year.

Previous reports indicated that TSMC is expected to have sole production responsibility for Apple's upcoming A12 chip and its variants expected to debut in new iPhone and iPad products starting this fall. The 7nm node (referred to as CLN7FF, 7FF, or simply N7) is expected to have an approximate 40 percent power and area

benefit over TSMC's 10nm FinFET process, utilized in Apple's A11 processors.

Additionally, as reported by

EETimes, TSMC has offered insight into its technology roadmap, both for its silicon processes and for its device packaging technologies. TSMC is

believed to have wrested sole ownership of production for Apple's processors away from the dual-sourcing arrangement with Samsung due to its advancements in wafer-level packaging. (What also went largely unnoticed at the time was TSMC's introduction of

land-side capacitors attached directly to the substrate.)

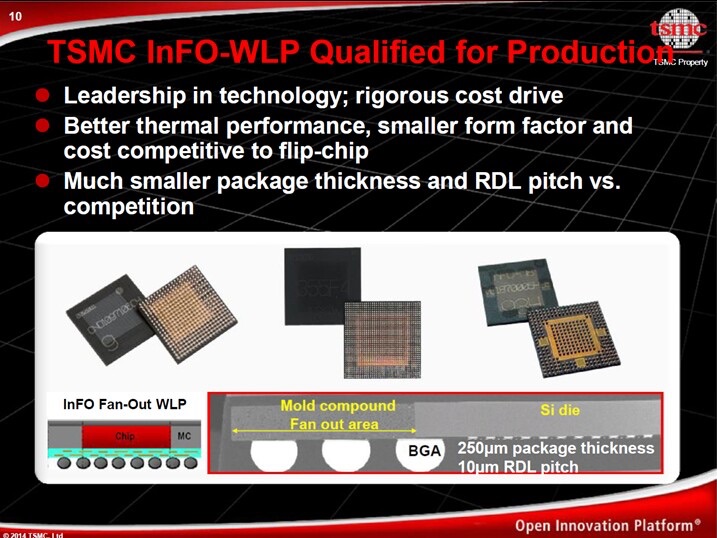

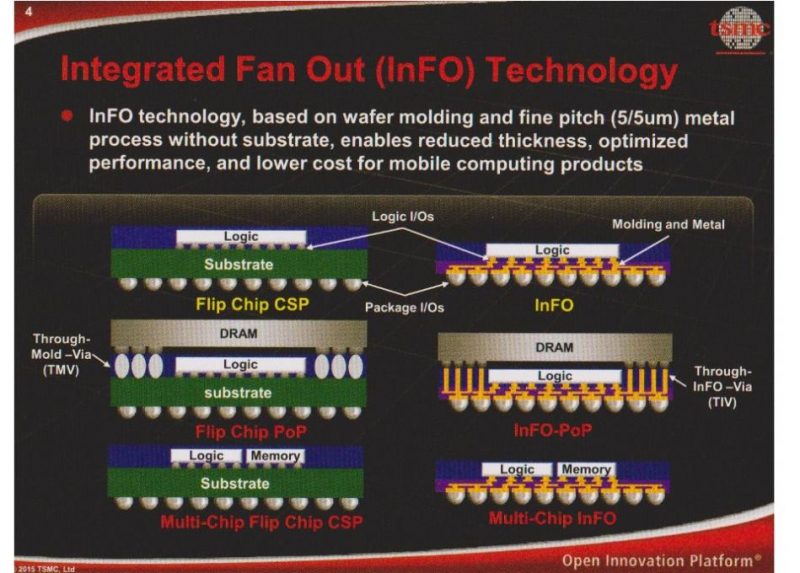

Building on the packaging leadership established with its InFO packaging offerings, TSMC has now announced six new packaging types aimed at a variety of devices and applications.

The InFO technique is getting four cousins. Info-MS, for memory substrate, packs an SoC and HBM on a 1x reticle substrate with a 2 x 2-micron redistribution layer and will be qualified in September.

InFO-oS has a backside RDL pitch better matched to DRAM and is ready now. A multi-stacking option called MUST puts one or two chips on top of another larger one linked through an interposer at the base of the stack.

Finally, InFO-AIP stands for antenna-in-package, sporting a 10% smaller form factor and 40% higher gain. It targets designs such as front-end modules for 5G basebands.

But that’s not all. TSMC introduced two wholly new packaging options. A wafer-on-wafer pack (WoW) directly bonds up to three dice. It was released last week, but users need to ensure that their EDA flows support the bonding technique. It will get EMI support in June.

Finally, the foundry roughly described something that it called system-on-integrated-chips (SoICs) using less than 10-micron interconnects to link two dice, but details are still sketchy for the technique to be released sometime next year. It targets apps from mobile to high-performance computing and can connect dice made in different nodes, suggesting it may be a form of system-in-package.

The announcement of these packaging technologies is important because they will enable a variety of different package and interconnect structures for Apple's SoCs, with the immediate benefit being novel interfaces to in-package memory. While InFO offers height, performance and thermal advantages for Apple, they still must interconnect to the RAM seated on top of the application processor through the use of wire bonds in a package-on-package configuration.

This interface presents thermal challenges and limits the width and speed of the memory bus interface due to the type of interconnects. The IC industry has seen quite a bit of effort into novel memory technologies such as

High Bandwidth Memory (HBM), but this technology has largely been relegated to graphics processors aimed at scientific, research, and extreme enthusiast use due to the high cost and low yield associated with the silicon interposers that enable the chip-to-memory connections. The fact that TSMC has unveiled a variant of InFO directly aimed at this solution bodes well for its increased adoption in the industry in a variety of products.

The InFO-oS process is of much more near-term interest for mobile device makers such as Apple, where the memory bus widths would be much lower, but the per-pin bandwidth is much higher, as seen in LPDDR4. According to a

TSMC report, the "oS" portion this technology refers to on-substrate, where die-partitioning would take place.

This would seem to allow for a 2.5D solution where the memory die is placed alongside the processor die as opposed to suspended above via a mold compound as seen in the original InFO-WLP packaging, enabling the higher interconnect density. However, the retention of a redistribution layer means a mold compound must still be in play, so a more thorough technical disclosure could help eliminate some of the ambiguity with this naming convention. While this would eliminate die-stacking, it would increase the total footprint of the packaged solution, which would still be a concern in a size-constrained mobile package.

<center>

TSMC InFO variants</center>

While Apple could eventually move to an HBM solution, which affords much greater memory bandwidth at lower power levels, the wafer-on-wafer (WoW) announcement is a genuine step towards true 3D integrated circuits, where eventually dies would be stacked directly on top of each other and interconnected through vias placed directly in the IC die.

The innovation for TSMC here would be in exactly how it packages these dies together, and what the interfaces look like as well as what type of redistribution layers (RDLs) they offer. While not directly applicable to Apple's line of processors, the InFO-AIP is also an important development, as radio frequency (RF) front-ends stand to take on another order of complexity with their adoption of much wider frequency bandwidths needed for 5G standards.

Beyond the 7nm node, TSMC also shared its outlook for the foundry's successive nodes, 7nm+ and 5nm. 7nm+ will be TSMC's first node to feature extreme ultraviolet (EUV) lithography, which stands to simplify the mask process by eliminating the need for multiple patterning in many areas to define smaller features.

Following 7nm+ will be 5nm, which would enter risk production late next year if current timelines hold, meaning volume production would occur sometime in 2020, though likely too late for a fall 2020 product launch, even with the most optimistic timelines. Though EUV has been long-awaited and will solve many problems in the industry, it brings a host of its own issues and will not bring huge performance jumps in successive nodes, nor will it grant smoother node transitions, as 5nm already presents its

own EUV challenges.

The node delivers 35% more speed or uses 65% less power and sports a 3x gain in routed gate density. By contrast, the N7+ node with EUV will only deliver 20% more density, 10% less power, and apparently no speed gains — and those advances require use of new standard cells.

Still, the above news is encouraging, as Apple should be able to enjoy the benefits of a new technology node for at least two out of the next three years. This will offer a boost as its processor architecture gains slow down, and the advent of new packaging techniques will allow Apple to overcome bandwidth and thermal constraints in ways that were simply not possible before.

TSMC has also offered hope for the future, painting the picture beyond 5nm in broad strokes with plans for newer transistor topologies such as silicon nanowires, and moving beyond silicon as the prime semiconducting medium to materials that ultimately offer higher carrier (electrons and holes) mobility.

TSMC also detailed ways to improve the conductivity and reduce the parasitics associated with the interconnects present in the silicon die. Ultimately, these interconnects often dictate how quickly transistors can switch due to the effective line load on them, and that is a concern all the way from the die to the package and on to the PCB. TSMC seems to be diligently pursuing a variety of solutions for its customers on two of those fronts, and its packaging solutions are bringing more and more of those PCB components straight into the device package to combat the third element.

<div class="linkback">Tags:

TSMC,

A12</div>

Discuss this article in our forums

<div class="feedflare">

<img src="[url]http://feeds.feedburner.com/~ff/MacRumors-Front?d=yIl2AUoC8zA" border="0"></img>[/url]

<img src="[url]http://feeds.feedburner.com/~ff/MacRumors-Front?d=6W8y8wAjSf4" border="0"></img>[/url]

<img src="[url]http://feeds.feedburner.com/~ff/MacRumors-Front?d=qj6IDK7rITs" border="0"></img>[/url]

</div><img src="

http://feeds.feedburner.com/~r/MacRumors-Front/~4/0ik5c54sWbQ" height="1" width="1" alt=""/>

Source:

TSMC Details Technology Roadmap With Multiple Offerings to Benefit Future Apple Devices